# Le Temps des Cerises: Efficient Temporal Stack Safety on Capability Machines using Directed Capabilities

AÏNA LINN GEORGES, Aarhus University, Denmark ALIX TRIEU\*, ANSSI, France LARS BIRKEDAL, Aarhus University, Denmark

Capability machines are a type of CPUs that support fine-grained privilege separation using *capabilities*, machine words that include forms of authority. Formal models of capability machines and associated calling conventions have so far focused on establishing two forms of stack safety properties, namely local state encapsulation and well-bracketed control flow. We introduce a novel kind of *directed* capabilities and show how to use them to make an earlier suggested calling convention more efficient. In contrast to earlier work on capability machine models we do not only consider integrity properties but also confidentiality properties; we provide a unary logical relation to reason about the former and a binary logical relation to reason about the latter, each expressive enough to reason about temporal stack safety. While the logical relations are useful for reasoning about concrete examples, they do not on their own demonstrate that stack safety holds for a large class of programs. Therefore, we also show full abstraction of a compiler from an overlay semantics that internalizes the calling convention as a single call step and explicitly keeps track of the call stack and frame lifetimes to a base capability machine. All results have been mechanized in Coq.

#### 1 INTRODUCTION

Lack of memory safety is an important source of security bugs, for instance, 70% of all issues in Microsoft products [Thomas 2019] and in the Google Chrome browser [Chromium 2020] are memory safety related. It is thus not surprising that a large number of software or hardware protection mechanisms such as shadow stacks, stack canaries, address space layout randomization, etc (see [Szekeres et al. 2013] for a survey) have been proposed. Capability machines have recently risen as a promising solution to memory safety vulnerabilities; quoting a Microsoft study, "[capability machines] would have deterministically mitigated at least two thirds of all those issues" [Joly et al. 2020].

Capability machines are a kind of architecture that enable fine-grained memory protection using tagged memory [Carter et al. 1994; Dennis and Van Horn 1966; Levy 1984] and *capabilities*, a form of unforgeable memory pointers with a certain amount of authority, in the form of a permission, range, etc. Over the last decade, CHERI [Watson et al. 2020], a family of capability machines, has matured into an extensive design featuring, among other, a full UNIX-style operating system, CheriBSD [Watson et al. 2015]. Ideas from CHERI are currently being adopted by ARM in their Morello project [Arm 2021], which is aimed at developing concrete CPU designs and prototypes that could be implemented in future hardware.

One of the promises of capability machines is that they can enforce security properties that we expect from high-level languages, in particular stack safety, even when machine code is linked with other untrusted and possibly adversarial machine code. This potential is not yet realized in practice. In particular, while CheriBSD does make use of so-called local capabilities to limit the impact of potential bugs, it does not rely on them for enforcing security properties. This is likely because a secure calling convention based on local capabilities could be too inefficient as it would require a

Authors' addresses: Aïna Linn Georges, Aarhus University, Denmark, ageorges@cs.au.dk; Alix Trieu, ANSSI, France, alix.trieu@ssi.gouv.fr; Lars Birkedal, Aarhus University, Denmark, birkedal@cs.au.dk.

<sup>\*</sup>This work was carried out while the author was affiliated with Aarhus University.

lot of stack clearing. Indeed, this is the case for the first known provably secure calling convention based on local capabilities [Skorstengaard et al. 2019a] — this calling convention requires to clear the full stack before and after every call. This has led to research on other calling conventions based on novel forms of capabilities. In particular, Skorstengaard et al. [2019b] proposed a calling convention based on so-called linear capabilities, which, however, are believed not to be efficiently implementable in hardware. This motivated another proposal by Georges et al. [2021] who suggested a secure calling convention based on a combination of so-called uninitialized capabilities and local capabilities, and which only involves a modicum of stack clearing per call, on the order of a single stack frame.

The works cited above on provably secure capability-machine-based calling conventions have all focused on spatial memory safety, in particular local state encapsulation and well-bracketed control flow. In another direction, Tsampas et al. [2019] recently proposed a kind of capabilities including "lifetime" information to enforce temporal memory safety, e.g., that the content of popped stack frames cannot be accessed. However, one problem with implementing this proposal is that in order to allow for a call depth of size  $2^n$ , n bits would be required in the encoding of the lifetime information for a capability, which renders it impractical.

In this paper, we propose a novel kind of so-called *directed* capabilities and show how they can be used in combination with uninitialized capabilities to realize a new calling convention, which is efficient (it does not involve any stack clearing at all) and which provably enforces both spatial and temporal stack safety properties.

More precisely, we present CeriseM, an extension of the low-level capability machine model of Georges et al. [2021], with a novel form of directed capabilities, for which we present a novel stack-based calling convention. We show that it provably guarantees spatial and temporal stack safety. In light of the fact that it is actually quite subtle to capture stack safety properties formally, as also emphasized in a recent paper by Anderson et al. [2021], we include a detailed discussion of the stack safety properties we consider and how our novel approach improves over earlier proposals, see § 2. We include a discussion of the impact of stack objects on stack safety properties; prior work on local capability machines have largely ignored stack objects, but they have a significant impact on the guarantees provided by the capability machine. In contrast to the earlier formal models for capability machines mentioned above, we do not only consider integrity properties but also (stack) confidentiality properties.

To formally establish *integrity*, we follow the approach of Skorstengaard et al. [2019a] and develop a unary Kripke logical relations model, which captures capability machine safety. Our model is an extension of the one by Georges et al. [2021]; the novelty consists of an extension to account for temporal safety. There are two facets to this: a simple one, which is to extend the definition to also treat directed capabilities, and a challenging one, which is to extend the model, in particular, the Kripke worlds, to capture the enforcement of temporal properties. The latter means that our model makes use of a novel kind of state transition system for the Kripke worlds.

To formally establish *confidentiality*, we further develop a *binary* logical relations model. We show that the binary logical relation implies contextual refinement so that it can serve as a sound proof method for establishing contextual equivalence and hence confidentiality. To the best of our knowledge, this is the first binary logical relations model for a low-level capability machine model.

We demonstrate that the unary and binary logical relations models can be used to prove stack safety properties for challenging example programs; we focus on examples that have not been considered in the literature before.

To give further evidence for the claim that our novel directed-capability-based calling convention actually does capture stack safety, we follow the approach of Skorstengaard et al. [2019b] and show full abstraction of a compiler from an overlay semantics that internalizes the calling convention as a

single call step and explicitly keeps track of the call stack and frame lifetimes to the base capability machine. The idea is that the overlay semantics clearly enforces stack safety; our overlay semantics is related to the one used in [Skorstengaard et al. 2019b] but now accounts for temporal properties by completely removing popped stack frames from the stack once their lifetime is over (technical differences are detailed in § 6).

We have mechanized all of the models and results presented in the paper on top of the mechanization of the Iris program logic [Jung et al. 2016, 2018, 2015; Krebbers et al. 2017a] in Coq [Krebbers et al. 2017b]. The Iris-Coq mechanization can be found online at https://github.com/logsem/cerise-stack-monotone.

# 2 ON THE STACK SAFETY OF CAPABILITY MACHINES

In this section, we explore the properties that make up stack safety in the context of capability machines. We follow Anderson et al. [2021], who define multiple degrees of stack safety, as various conjunctions of local state encapsulation (LSE) and well-bracketed control flow (WBCF). In particular, our goal is to reach a notion of stack safety that falls within their definition of observational stack safety, which also covers the temporal aspect of LSE. A key takeaway of this section is to highlight how existing calling convetions incur undesired overhead in order to enforce stack safety. Unlike Anderson et al. [2021], we consider LSE, WBCF and temporal stack safety for machines with both a stack and a heap. For clarity, we illustrate each property with an example written in a C-like language, though we actually consider the underlying assembly code. Next, we explore two interesting aspects of these properties that are particularly tricky. Finally, we survey previously proposed capability machine calling conventions and show where they fall on the spectrum of stack safety, including the novel calling convention and efficient enforcement mechanism we present in this paper.

# 2.1 A Family of Stack Safety Properties

```

void adv(void);

void f(void) {

int *y; // allocated on

*y = 2; // the stack

adv();

assert (*y == 2); }

```

Listing 1. Integrity: frame

```

void adv(void);

void f(void) {

static int x = 2;

adv();

assert (x == 2); }

```

Listing 2. Integrity: environment

```

1

void adv(void);

2

void f(void) {

3

int *y; *y = 2;

adv();

4

5

return; }

void g(void) {

6

int *y; *y = 3;

8

adv();

return; }

```

Listing 3. Confidentiality: frame private state x.

2.1.1 Local State Encapsulation. Local state is a concept that exists in both low and high level languages. In a low-level language with a stack, local state often refers to the encapsulation of local variables in a stack frame. For instance, in Lis. 1, the local variable y is a part of f's local stack frame, and is not shared with the arbitrary adversarial code adv; and hence the assert, stating the integrity of y, should succeed.

In high-level languages, local state may also refer to the state encapsulated within the scope of a closure. Consider Lis. 2, where function f possesses some private state x (a static variable persists across calls, similarly to local variables in closures). Upon return, the integrity of x is tested with an assert statement. If x is not properly encapsulated, adv may modify x, and the assertion fails.

The stack is used to store local variables as well as the local environment to be reclaimed upon return of a call. When discussing LSE, we will refer to the local state being the local stack frame not shared with a callee, as well as the state encapsulated within a closure, which ought to stay encapsulated not just from the callee, but from the caller as well. For instance, an adversarial context may call f in Lis. 2 multiple times, but it should never get access to the

Following Anderson et al. [2021], we must distinguish between local state integrity and local state confidentiality. Local state integrity states that the local stack frame is protected from changes by the callee, local state confidentiality states that the local stack frame cannot be read by the callee and thus influence their behaviour. Hence local state confidentiality is a binary property.

```

void adv(void);

void f(void) {

2

3

static int x = 2;

adv(); }

void g(void) {

5

static int x = 3;

adv(); }

```

Listing 4. Confidentiality: environment

```

void adv(void);

2

void f(void) {

static int x = 0;

3

4

x = 0; adv();

x = 1; adv();

5

assert (x == 1); }

```

Listing 5. Awkward Example

For example, Lis. 3 contains two programs f and g with different local states that should stay hidden from the arbitrary function adv. Local state confidentiality guarantees the contextual equivalence of the functions f and g. Similarly, Lis. 4 depends on the same local state confidentiality, but for the environment of closures.

Since we also use the stack for the encapsulated environment of closures, our notion of LSE includes the integrity and confidentiality of the environment of a closure against the full context. Indeed, a closure needs to protect its private state against *both* callees and callers.

> Well-bracketed Control flow. Another common property in high-level languages is well-bracketed control flow. For example, consider Lis. 5, which is a variant of the classical "awkward example" [Dreyer et al. 2010a]. Here f possesses some local state x (line 3), which is set to 0 before calling some arbitrary adversarial code adv(). After the call returns, x is set to 1 before calling the

adversary again. Finally, x is checked to be still equal to 1 at the end. If WBCF is not enforced, then during the second call to adv on line 5, adv could store the return pointer to line 6 in its own private state, and call f, which would then set x to 0 before calling adv again who can finally use the return pointer to line 6 it kept and fail the assertion.

It has been shown that both some form of LSE and WBCF can be enforced on capability machines, even in the presence of arbitrary code [Georges et al. 2021; Skorstengaard et al. 2018, 2019b]. We will give more details on how this is enforced in § 3.2.

```

void h(int*x) { *x = 0; }

2

3

void g(int* x) {

char* t[K];

5

h(x);

6

void f(int** x) {

char* t[N];

int z;

8

9

*x = &z; }

10

int main(void) {

int* x;

11

12

f(&x);

13

g(x);

return 0; }

```

Listing 6. Example violating temporal stack safety

Temporal Stack Safety. In another direction, Tsampas et al. [2019] study the issue of temporal safety. Consider the code in Lis. 6<sup>1</sup>, where &x on line 12 is a pointer to a location containing another pointer. After the call to f, there is now a pointer at &x to the location 1 previously occupied by z on line 8. The value of 1 depends on a global variable N. It should be noted that 1 is stale after the return and should not be allowed to be passed down. Nevertheless, 1 is passed to h through g. For well chosen values of K and N, it is possible that 1 coincides with where the return pointer of h is stored and thus the store at line 2 can lead to the control flow being hijacked. This example shows a temporal stack safety violation that exploits a dangling stack pointer. To address this

issue, Tsampas et al. propose that capabilities are extended with "lifetime" information, basically the call depth of the function's stack frame, and that capabilities with longer lifetime may not be used to store a capability with shorter lifetime. This would disallow the store on line 9 in the example. In essence, it disallows dangling stack pointers to be stored on the stack, and thus to be passed down the call stack beyond their lifetime.

Also related to temporal stack safety, Anderson et al. [2021] find that the lazy tagging and clearing micro-policy of Roessler and DeHon [2018] violates the temporal aspect of observable stack safety, and repairs it by generating fresh identifiers for each call, requiring an unbounded number of tags.

<sup>&</sup>lt;sup>1</sup>An example adapted from [Tsampas et al. 2019].

# 2.2 Two Subtleties of Stack Safety

```

int g(char* z, char* in)

void f(void) {

void f(void) {

int f(char* in) {

2

static int x = 2;

int *x; *x = 2; }

3

int *y;

3

void g(void) {

3

int *y = 2;

*y = &x;

int *x; *x = 3; }

char* z = ...;

4

4

4

assert (x == 2); }

5

g(z, in);

assert (y == 2); }

Listing (8) Temporal confiden-

6

Listing (7) Dangling stack

```

Listing (7) Dangling stack tiality Listing (9)

Listing (9) Integrity with stack objects

We now highlight two subtleties of stack safety which previous works have mostly glossed over in the context of capability machines.

2.2.1 Elaborating on Temporal Stack Safety. Stack frame lifetime intuitively dictates that the content of a popped frame should not be read once popped. Tsampas et al. define temporal stack safety as the absence of dangling stack pointers passed down the call stack (cf. Lis. 6). Here we wish to emphasize that the absence of dangling stack pointers should also mean that no caller should be able to (re)gain access to a dangling stack pointer when they resume. Concretely, consider Lis. 7, where f possesses some local state x, initialised to 2, which is copied to the local variable y, after which its integrity is tested with an assert statement. This assert statement appears entirely trivial. However, recall that x is statically allocated and that f may be called multiple times. Each invocation of f may therefore leave a copy of x's address on the stack. Subsequently, if a caller can read f's old stack frame then it may break the integrity of x in-between calls. This dangling stack attack is an additional threat in low level languages where callers may create activation records containing dangling stack pointers.

We will distinguish the absence of dangling stack pointers property from a slightly different notion of temporal stack safety, which we call *temporal confidentiality*, and which can be thought of as the temporal aspect of local state confidentiality. Consider two programs f and g whose only difference is to leave different traces on their respective stack frames, e.g., as in Lis. 8. Then, as long as temporal confidentiality is enforced, no caller should be able to distinguish f from g. We remark that the complete absence of any dangling stack pointer (passed down or otherwise) implies temporal confidentiality, without having to clear any parts of the stack.

2.2.2 Stack Safety in the Presence of Stack Objects. We now explain how stack objects may influence stack safety properties. In prior work on local capability machines, stack objects have largely been ignored. However, they have a significant impact on the guarantees provided by the capability machine. Disallowing stack objects altogether is too restrictive as it is a common programming idiom in C-like languages to pass stack references as arguments.

Let us consider what happens to local state integrity in the presence of stack objects. Consider for instance the example in Lis. 9 in which f receives an input from a caller and passes it along with its own stack object to its callee. In this scenario, neither f's caller, nor g are trusted. In fact, they may collaborate to break y's integrity. Indeed, if no precaution is taken by f, it may be possible that the stack object passed by its caller actually possesses *write* authority on f's stackframe, which could be abused by g.

# 2.3 Enforcing Stack Safety in Capability Machines

Let us recap the stack safety properties we have isolated thus far. (1) *Local state integrity* (LSE integrity) guarantees that a callee cannot break the integrity of local stack frames (Listings 1 and 9), and that neither the callee nor a caller can break the integrity of the private environment associated with a closure (Lis. 2). (2) *Local state confidentiality* (LSE confidentiality) guarantees that the local stack frame cannot influence the behaviour of a callee (Lis. 3), and that the private environment of a closure cannot influence the behaviour of a callee or a caller (Lis. 4). (3) *Well-bracketed control flow* (WBCF) guarantees that a callee returns to its immediate caller in the call stack (Lis. 5). (4)

|                       | LOCAL + clear |   | LOCAL + U |   | LINEAR         |                       | TEMPORAL |     | DIRECTED + U |   |

|-----------------------|---------------|---|-----------|---|----------------|-----------------------|----------|-----|--------------|---|

|                       | w\o           | w | w\o       | w | w\o            | w                     | w\o      | w   | w\o          | w |

| LSE integrity         | ✓             | Х | ✓         | Х | $\checkmark^2$ | <b>√</b> <sup>2</sup> | N\A      | N\A | ✓            | Х |

| LSE confidentiality   | ✓             | Х | ✓         | Х | $\checkmark^2$ | √2                    | N\A      | N\A | ✓            | Х |

| WBCF                  | ✓             | Х | ✓         | Х | ✓              | ✓                     | N\A      | N\A | ✓            | Х |

| Temp. confidentiality | ✓             | ✓ | ✓         | ✓ | Х              | Х                     | N\A      | N\A | ✓            | ✓ |

| Dangling stack        | Х             | Х | Х         | Х | ✓              | ✓                     | ✓        | ✓   | ✓            | ✓ |

Table 1. Guarantees granted by the calling convention.

Temporal stack safety according to Tsampas et al. guarantees that a callee cannot return a dangling stack pointer (a property that is violated in Lis. 6). We expand on that notion and additionally guarantee that no caller can restore a dangling stack pointer upon return either (Lis. 7). Finally (5) temporal confidentiality guarantees that a caller is unable to read popped stack frames, or, in other words, that popped stack frames cannot influence the behaviour of the caller (Lis. 8). Temporal confidentiality can also be interpreted as the temporal aspect of local state confidentiality.

Each of these properties can be investigated with or without the presence of stack-object parameters. It is in general easier to guarantee these properties by altogether disallowing stack objects. Passing a stack object from a caller to a callee is not safe, unless certain conditions are dynamically checked in between, in case an overlapping stack pointer (potentially breaking integrity) can be reached from that stack object.

Together, these properties make up Anderson et al.'s notion of observable stack safety. In order for the calling convention of a capability machine to be fully stack safe, it must enforce each of these properties. Unfortunately, the current state of the art enforce them at a varying degree of efficiency. In particular, enforcing temporal stack safety appears always to come at a significant cost.

Table 1 relates previous work on capability machine stack safety and also the work presented in this paper to these properties, each in a situation where stack objects are not passed from caller to callee (w\0), and in a situation stack objects are allowed (w). A  $\checkmark$  means that the property is guaranteed by the associated calling convention. The different calling conventions have more or less overhead, in terms of the amount of stack clearing required by the calling convention. A  $\checkmark$  depicts a high overhead, on the order of the full stack size, a ✓ depicts a relatively low overhead, on the order of a single stack frame, and a  $\checkmark$  depicts a low overhead of constant time. A X means some additional check is needed to guarantee the property (it does not mean it is impossible to guarantee a given property, but rather that it requires some additional mechanism beyond the calling convention). Finally, N\A means that the property is assumed to hold given the granularity of the capability machine language. (The marks come from our understanding of the earlier work, supported by the various examples verified in each model.) The first column outlines the calling convention using LOCAL capabilities and full stack clearing [Skorstengaard et al. 2018]. The second column outlines the calling convention using uninitialized capabilities and partial clearing [Georges et al. 2021]. The third column outlines the calling convention using LINEAR capabilities [Skorstengaard et al. 2019b], and the fourth column outlines a more high level language using TEMPORAL capabilities [Tsampas et al. 2019]. The rightmost column gives an overview of the novel calling convention using the **DIRECTED** capabilities we introduce in this paper.

We remark that the LINEAR column shows a calling convention that checks many of the boxes and, in fact, we conjecture that a (LINEAR + uninitialized)-based calling convention could check all boxes. Thus the reader may wonder why we introduce a new kind of capability and a new calling

<sup>&</sup>lt;sup>2</sup>While we mark the StkTokens calling convention [Skorstengaard et al. 2019b] as enforcing LSE as the authors claim, it is actually unclear whether it does protect more than just the local stackframe as done in the other works [Georges et al. 2021; Skorstengaard et al. 2018]. Indeed, the calling convention does not seem to prevent one from leaving a capability to some private state on the stack and returning without clearing the stackframe.

```

≜ [0, AddrMax]

a \in Addr

\in RegName ::= pc | r<sub>0</sub> | r<sub>1</sub> | ...

::= O | E | RO | RX | RW | RWX

p \in Perm

RegName \rightarrow Word

reg \in Reg

| RWL | RWLX | URW | URWL | URWX | URWLX

Addr \rightarrow Word

∈ Mem

€ Locality ::= GLOBAL | LOCAL | DIRECTED

∈ ExecConf ≜

Reg \times Mem

\triangleq \{(p, q, b, e, a) \mid b, e, a \in Addr\}

∈ ExecMode ::=

c \in Cap

\triangleq \mathbb{Z} + Cap

w \in Word

Executable | Halted | Failed

\rho \in \mathbb{Z} + \text{RegName}

i ::= jmp \ r \mid jnz \ r \ r \mid move \ r \ \rho \mid load \ r \ r \mid store \ r \ \rho \mid add \ r \ \rho \ \rho \mid sub \ r \ \rho \ \rho \mid

lt r \rho \rho | lea r \rho | restrict r \rho | subseg r \rho \rho | isptr r r | getp r r | getl r r |

getb r r \mid gete r r \mid geta r r \mid fail | halt | loadU r r \rho \mid storeU r \rho \rho \mid promoteU r \mid

Fig. 2. Machine words, machine state and instructions.

```

ExecStep  $(\text{Executable, } \varphi) \rightarrow \left\{ \begin{array}{l} \llbracket decode(z) \rrbracket(\varphi) & \text{if } \varphi.\text{reg}(\text{pc}) = (p,g,b,e,a) \land b \leq a < e \land \\ p \in \{\text{RX}, \text{RWX}, \text{RWLX}\} \land \varphi.\text{mem}(a) = z \\ \text{(Failed, } \varphi) & \text{otherwise} \end{array} \right.$

convention here. There are several reasons: first, linear capabilities can be cumbersome to use, as only the top part of a stack frame can be passed as parameters. Second, exceptions cannot be implemented efficiently. Third, and most importantly, LINEAR capabilities are expensive to realize in practice. Moving a LINEAR capability requires an atomic move which is believed by hardware developers to lead to an undesirable overhead in runtime [Skorstengaard 2019, §3.6.2]. Indeed, this was also the reason why Georges et al. [2021] considered local and uninitialized capabilities instead.

In fact, in order to reach full stack safety à la [Anderson et al. 2021], there is a cost to each existing calling convention. The excessive stack clearing of [Skorstengaard et al. 2018] was improved upon in [Georges et al. 2021], however the latter only achieves temporal stack safety by clearing local stack frames upon return. Tsampas et al. [2019] propose temporal capabilities as an enforcement mechanism to prevent dangling stack pointers. However, they would require an expensive amount of bits to represent.

In this paper, we propose directed capabilities as an *efficient* enforcement mechanism (both wrt. space and time complexity) of full stack safety. § 3.3 presents the definition of directed capabilities, and in § 4 to 6 we show how directed capabilities can be used to enforce stack safety. Our calling convention does not use any stack clearing at all. Furthermore, directed capabilities can be efficiently realized in practice, requiring only one additional bit in the representation of capabilities, and with only one additional dynamic bounds check which is similar to existing ones (and hence efficient).

We define a unary model to reason about integrity properties, and a binary model to reason about confidentiality properties (including temporal confidentiality). We use these models to reason about small but challenging examples; we focus on examples that depend on properties not previously considered on a low level capability machine (integrity in the presence of stack objects, and temporal confidentiality). Furthermore, we follow the methodology presented by Skorstengaard et al. [2019b] and define an overlay semantics that clearly enforces each of the properties in Table 1. In § 6.2, we show how our new calling convention is fully abstract with respect to this overlay semantics.<sup>3</sup>

<sup>&</sup>lt;sup>3</sup>In light of this full abstraction result, the reader may wonder why we also develop the logical relations models. The reason is that while the overlay semantics makes some properties obvious (e.g., popping stack frames upon return), it is not easy to use the overlay semantics for reasoning about concrete examples. This is not so surprising: even for high-level languages like ML, scientists have had to invent Kripke logical relations (and other kinds of) models to reason about local state encapsulation, e.g., [Ahmed et al. 2009; Dreyer et al. 2010a; Sumii and Pierce 2007].

# 3 CAPABILITY MACHINE: OPERATIONAL SEMANTICS AND CALLING CONVENTION

In this section we present the operational semantics of the capability machine we consider. Our capability machine is based on the one by Georges et al. [2021] and is, transitively, inspired by CHERI [Watson et al. 2015] and the M-Machine [Carter et al. 1994].

In § 3.1, we first recall from Georges et al. [2021] how the operational semantics for a capability machine with local and uninitialized capabilities is defined. Then, in § 3.2, we further recall how said capabilities can be used to enforce LSE and WBCF via a secure calling convention. We then add support for directed capabilities in § 3.3, and present our new improved calling convention, which can finally *efficiently* guarantee temporal stack safety, in § 3.4. Figures 2 to 5 summarize the operational semantics; components marked in blue are for the novel directed capabilities and will be detailed in § 3.3.

Fig. 2 describes the syntax of our capability machine. We model a capability machine with finite memory. The set of addresses Addr is defined as the interval [0, AddrMax], where AddrMax is the top address and cannot be dereferenced. Memory contains machine words w that are represented by either an (unbounded) integer or a capability. A capability is a quintuple (p, g, b, e, a) representing the authority to exert the permission p over the memory range [b, e[ and currently pointing to a.

#### 3.1 A Capability Machine with Local and Uninitialized Capabilities

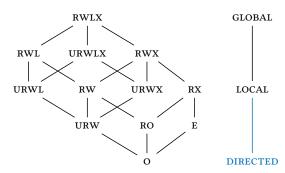

A permission p can either be opaque (0), enter (E), read-only (RO), read-execute (RX), read-write (RW), read-write-execute (RWL), read-write-local (RWL), read-write-local-execute (RWLX), or uninitialized-RW (URW), uninitialized-RWL (URWL), uninitialized-RWX (URWX), uninitialized-RWLX (URWLX). Permissions form a lattice as illustrated in Fig. 4. The permissions RO, RX, RW, RWX are standard. Permission o provides no authority. Enter (E) capabilities represent opaque closures encapsulating code and data. As such, they cannot be read, written to, executed nor modified. They can only be jumped to, which will load them into the program counter register and unseal them into a RX capability. Their usage will be further illustrated when describing the operational semantics and the calling convention. Locality q is either GLOBAL or LOCAL, and forms a lattice as illustrated in Fig. 4. LOCAL capabilities are meant to represent stack derived capabilities, while GLOBAL ones represent heap derived ones. They will be described further in § 3.2. Write-local permissions (RWL and RWLX) are similar to their regular counterparts, but additionally provide the authority to write LOCAL capabilities to memory. That is, a regular RW capability cannot be used to write a LOCAL capability to memory, only GLOBAL ones. Finally, uninitialized capabilities  $u\pi$  represent a form of use-after-write authority: they provide permission  $\pi$  over the range [b, a[ and write permission on range [a, e] — the boundary is automatically increased when the capability is used to write at a.

Fig. 4. Permission and locality hierarchy.

Machine instructions i operate over registers or constants and their behaviour will be detailed later. A register is either the program counter pc or a general purpose register  $r_0, r_1, \ldots$  A machine state is composed of a mode describing whether the machine is in an Executable state, or in a terminal Failed or Halted state, and an execution configuration. An execution configuration is a pair of a register file, mapping registers to their values, and a memory state, mapping addresses to their values.

The operational semantics of the machine shown in Fig. 3 is given in smallstep style and has only

one rule: if the state is Executable and the program counter contains an in-bounds executable capability pointing to some machine word, then an instruction is decoded and executed; otherwise the machine fails. Recall that, in general, failing is considered safe since it crashes the machine before anything unsafe occurs.

The semantics of instructions is given in Fig. 5. Most instructions increment the program counter at the end of their execution, except for branching and terminating instructions. This process is defined by updPC, which fails if the program counter does not contain an executable capability. Terminating instructions fail and halt change the machine state respectively to a Failed and Halted state. The move instruction copies a machine word in a register. The load instruction reads from the memory into a register, provided that a capability with sufficient authority is given. Similarly, the store instruction is used to write to memory. Additionally, if the word that is stored is a local capability, it must be that the capability provided has write-local authority. The jmp instruction copies a word to the program counter, additionally, if the word is an enter capability, it is unsealed into a RX one. The instructions restrict and subseg are used to decrease the authority of a capability. The former decreases the permission and the locality of a capability following the lattice given in Fig. 4. The latter decreases the range of authority of a capability. The lea instruction is used to change the current address a capability points to. As explained earlier, an enter capability cannot be modified, and subseg and lea will thus fail. Furthermore, as the current address of an uninitialized capability indicates the boundary between where its regular authority applies and where it can only write, it is only safe to decrease the current address using lea. The instructions getp, getl, getb, gete and geta can be used to retrieve respectively the permission, locality, base address, end address and current address of a capability. loadU and storeU are similar to their regular counterparts, but operate only with uninitialized capabilities. An additional offset parameter is provided in order to be able to access the range that has already been written to. Moreover, if the offset provided is 0, then the boundary of the capability is incremented by storeU. The promoteU instruction can promote an uninitialized capability to its regular counterpart by discarding the memory range that has not been written to yet.

# 3.2 A Secure Calling Convention using Local and Uninitialized Capabilities

We now give an intuitive account of how the calling conventions of Skorstengaard et al. [2018, 2019a] and Georges et al. [2021] enforce local state encapsulation and well-bracketed control flow. The calling convention of Skorstengaard et al. [2018] uses local capabilities (not uninitialized capabilities) and requires that a program is initially provided with a stack capability with authority over the whole stack in a register  $r_{stk}$  when executed. Assume the following scenario where Alice calls Bob who calls Claire. We explain how Bob can protect himself from both Alice and Claire using the calling convention of Skorstengaard et al. [2018].

Bob expects to receive a stack capability from Alice to build his own stack frame. Similarly, when calling Claire, Bob needs to provide the stack capability to her. However, in order to enforce local state encapsulation, it is necessary that Bob does not provide access to his own stackframe to Claire. Thus, when calling Claire, Bob restricts the stack capability to the unused part, using the subseg instruction, and then passes it to her. However, Bob needs to be able to restore access to his own stack frame upon return. He can do that using an enter capability: Bob constructs a return capability as an enter capability that restores the local environment when jumped to. This return capability can be safely passed to the callee Claire as its contents cannot be read, but can only be jumped to. This suffices to protect Bob's private state from Claire, but it is not enough to enforce WBCF. Indeed, on its own, this does not prevent the attack explained in § 2.1.2, in which a callee keeps a copy of a previous return capability beyond its "lifetime". To prevent this kind of attack, Skorstengaard et al. use local capabilities: The stack capability is made write-local, executable

$$\mathrm{updPC}(\varphi) = \left\{ \begin{array}{ll} (\mathsf{Executable}, \varphi[\mathsf{reg.pc} \mapsto (p, g, b, e, a + 1)]) & \text{if } \varphi.\mathsf{reg}(\mathsf{pc}) = (p, g, b, e, a) \text{ and } \mathsf{Rx} \not \leqslant p \\ (\mathsf{Failed}, \varphi) & \text{otherwise} \end{array} \right.$$

$$\operatorname{getWord}(\varphi,\rho) = \left\{ \begin{array}{ll} \rho & \text{if } \rho \in \mathbb{Z} \\ \varphi.\operatorname{reg}(\rho) & \text{if } \rho \in \operatorname{RegName} \end{array} \right. \\ \operatorname{canReadUpTo}(w) = \left\{ \begin{array}{ll} \bot_{\operatorname{ADDR}} & \text{if } w \in \mathbb{Z} \\ \min(a,e) & \text{if } w = (\updayscript{U}\pi, \_, \_, e, a) \\ e & \text{if } w = (\updayscript{\pi}, \_, \_, e, \_) \end{array} \right.$$

| i                          | $[i](\varphi)$                                      | Conditions                                                                                                    |

|----------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| fail                       | (Failed, $\varphi$ )                                |                                                                                                               |

| halt                       | $(Halted, \varphi)$                                 |                                                                                                               |

| move $r \rho$              | $updPC(\varphi[reg.r \mapsto w])$                   | $w = \text{getWord}(\varphi, \rho)$                                                                           |

| ,                          | 1 (12 0 3)                                          | $\varphi$ .reg $(r_2) = (p, q, b, e, a)$ and $w = \varphi$ .mem $(a)$                                         |

| load $r_1$ $r_2$           | $updPC(\varphi[reg.r_1 \mapsto w])$                 | and $b \le a < e$ and $p \in \{\text{RO, RX, RW, RWX, RWL, RWLX}\}$                                           |

| store $r  ho$              |                                                     | $\varphi$ .reg $(r) = (p, q, b, e, a)$ and $b \le a < e$ and                                                  |

|                            |                                                     | $p \in \{\text{RW}, \text{RWX}, \text{RWL}, \text{RWLX}\}\ $ and $w = \text{getWord}(\varphi, \rho)$ and      |

|                            | $updPC(\varphi[mem.a \mapsto w])$                   | if $w = (\_, LOCAL, \_, \_, \_)$ , then $p \in \{RWLX, RWL\}$ and                                             |

|                            |                                                     | if $w = (\_, DIRECTED, \_, \_, \_)$ , then $p \in \{RWLX, RWL\}$ and                                          |

|                            |                                                     | $canReadUpTo(w) \le a$                                                                                        |

| $jmp\;r$                   | (Executable,                                        | if $\varphi$ .reg $(r) = (E, g, b, e, a)$ , then $newPc = (RX, g, b, e, a)$                                   |

|                            | $\varphi[\text{reg.pc} \mapsto \textit{newPc}])$    | otherwise $newPc = \varphi.reg(r)$                                                                            |

| restrict $r \rho$          |                                                     | $\varphi$ .reg $(r) = (p, g, b, e, a)$ and                                                                    |

|                            | $\mathrm{updPC}(\varphi[\mathrm{reg}.r \mapsto w])$ | $(p',g') = \text{decodePermPair}(\text{getWord}(\varphi,\rho)) \text{ and}$                                   |

|                            |                                                     | $(p', g') \le (p, g) \text{ and } w = (p', g', b, e, a)$                                                      |

| subseg $r  ho_1  ho_2$     |                                                     | $\varphi.\operatorname{reg}(r) = (p, g, b, e, a) \text{ and for } i \in \{1, 2\},$                            |

|                            | $updPC(\varphi[reg.r \mapsto w])$                   | $z_i = \operatorname{getWord}(\varphi, \rho_i) \text{ and } z_i \in \mathbb{Z} \text{ and }$                  |

|                            |                                                     | $b \le z_1$ and $0 \le z_2 \le e$ and $p \ne E$ and $w = (p, g, z_1, z_2, a)$                                 |

| lea $r ho$                 | $updPC(\varphi[reg.r \mapsto w])$                   | $\varphi$ .reg $(r) = (p, g, b, e, a)$ and $z = \text{getWord}(\varphi, \rho)$ and                            |

|                            |                                                     | $p \neq E$ and $w = (p, g, b, e, a + z)$ $p = U$ -, then $z \le 0$                                            |

| geta $r_1$ $r_2$           | $updPC(\varphi[reg.r_1 \mapsto a])$                 | $\varphi.\operatorname{reg}(r_2) = (\underline{\ }\underline{\ }\underline{\ }\underline{\ }\underline{\ }a)$ |

| loadU $r_1$ $r_2$ $ ho$    |                                                     | $\varphi$ .reg $(r_2) = (p, g, b, e, a)$ and $p = U$ - and                                                    |

|                            | $updPC(\varphi[reg.r_1 \mapsto w])$                 | $off = getWord(\varphi, \rho) \text{ and } b \le a + off < a \le e \text{ and}$                               |

|                            |                                                     | $w = \varphi.\text{mem}(a + off)$                                                                             |

| storeU $r$ $ ho_1$ $ ho_2$ |                                                     | $\varphi$ .reg $(r) = (p, g, b, e, a)$ and $p = U$ - and                                                      |

|                            |                                                     | off = getWord( $\varphi$ , $\rho_1$ ) and $w$ = getWord( $\varphi$ , $\rho_2$ ) and                           |

|                            | $updPC(\varphi')$                                   | if $w = (\_, \ell, \_, \_)$ and $\ell \neq GLOBAL$ then                                                       |

|                            | $[\text{mem.}(a + off) \mapsto w])$                 | $p \in \{\text{URWLX}, \text{URWL}\}\ \text{and}\ b \leq a + off \leq a < e \ \text{and}$                     |

|                            |                                                     | if off $\neq 0$ then $\varphi' = \varphi$ else $\varphi' = \varphi[\text{reg.}r \mapsto (p, g, b, e, a + 1)]$ |

|                            |                                                     | and if $\ell = \text{DIRECTED}$ , then canReadUpTo(w) $\leq a + off$                                          |

| promoteU r                 | $updPC(\varphi[reg.r \mapsto w])$                   | $\varphi$ .reg $(r) = (p, g, b, e, a)$ and $p = U\pi$ and                                                     |

| 100 2002                   | (1 [9 "])                                           | $w = (\pi, g, b, \min(a, e), a)$                                                                              |

| •••                        |                                                     |                                                                                                               |

| _                          | (Failed, $\varphi$ )                                | otherwise                                                                                                     |

Fig. 5. Operational semantics: instruction semantics.

(RWLX) and LOCAL, and all other (heap) capabilities are non write-local. This guarantees that if the return capability is built on the stack (and therefore LOCAL), then the only place Claire can keep a copy of a return capability, is on the stack itself. Consequently, by clearing the stack before passing it to Claire, Bob can be sure that she will not be able to recover a previously left copy of a return capability. Finally, to protect himself from Alice, Bob also clears the whole stack and the registers before returning, so that Alice cannot access anything. Skorstengaard et al. later point out that it is sufficient for Bob to only clear his own stack frame, as anything that Claire may leave on the stack either originally came from Alice, or is a return capability from Bob, and, as Bob clears his own

stack frame, using the return capability will only lead to cleared data. As briefly mentioned in § 2, the original calling convention by Skorstengaard et al. [2018] enforces temporal confidentiality with an excessive amount of clearing. With the optimization by Skorstengaard et al. [2019a], one only clears one's own stack frame on return. Although this improves the efficiency of the calling convention, every secure closure must clear its own stack frame upon return.

Furthermore, even with the optimization mentioned by Skorstengaard et al. [2018], Bob still needs to clear the whole stack before being able to call Claire safely, and hence the calling convention is still very inefficient. To address this issue, Georges et al. [2021] proposed to make the stack capability into an uninitialized capability. By passing an uninitialized urwlx stack capability to Claire, we are guaranteed that Claire cannot read anything left on the stack, without overwriting it beforehand, and thus there is no need to clear the whole stack before calling Claire. However, Bob still needs to clear his own stack frame before returning, as there is no guarantee that Alice did not keep a "fully initialized" stack capability, which would allow her to read leftover data on the stack. For this calling convention, Georges et al. [2021] prove that LSE and WBCF are enforced; however dangling stack pointers are still a possibility, and thus some clearing is still needed in order to guarantee temporal confidentiality.

# 3.3 Directed Capabilities

We now introduce a novel kind of directed capabilities and then explain, in § 3.4, our new improved calling convention, which relies on directed capabilities to efficiently guarantee LSE, WBCF and temporal stack safety (as we prove in later sections).

The intention of directed capabilities is to restrict where they can be stored in memory. This is done by adding a new locality directed, as illustrated in the locality lattice in Fig. 4. To write a directed capability to memory it is then necessary to have permit-write-local authority (similarly to writing local capabilities to memory), as shown in the operational semantics of store and store of in Fig. 5. The distinguishing feature of a directed capability is that it cannot be stored below where it can read memory up to. That is, for a directed capability with a regular permission (i.e., not uninitialized) with authority over range [b, e[, it can only be stored at an address a such that  $a \le a$ . For an uninitialized directed capability  $(u\pi, \ell, b, e, a)$ , the part [a, e[ can only be written to, therefore it can only be stored at an address a such that  $a \le a$ . The intuition is that, for a stack that grows upwards, the address a stack capability can read up to implicitly approximates the lifetime of the capability. Given two directed capabilities, if the first can read at a lower address than the second, then the first is owned by an "older" stack frame than the second and has thus a longer lifetime.

We remark that, from an hardware implementation point of view, directed capabilities should be quite easy to implement. First, uninitialized directed capabilities require only two additional bits, one for the directed locality, and one indicating whether it is uninitialized. Since increased pointer size can severely affect performance, CHERI Concentrate [Woodruff et al. 2019] employs a rigorous compression scheme to achieve realistic performance. Within this scheme, 2 and 7 bits are reserved for future use in the CHERI-64 and CHERI-128 respective compression formats. The two necessary additional bits are thus already available in either format. We can contrast that to temporal capabilities [Tsampas et al. 2019], which require n bits to encode the lifetime information for a call depth of size  $2^n$ . The required number of bits is thus unbounded, and it is unclear how to determine the ideal least number of bits. Tsampas et al. discuss this exact point, and propose various workarounds. Directed capabilities, on the other hand, already fit within existing formats.

Second, directed capabilities only change the semantics of load(U) and store(U) by adding an extra bounds check. The added bounds check is no different from current checks, and we expect existing optimisation patterns, such as parallelisation, to apply.

# 3.4 A New Calling Convention using Directed Capabilities

Let us revisit the example in § 3.2, now assuming that the stack capability is directed instead of local. When Bob is called by Alice, Bob can ensure that Alice did not keep a capability with *read* authority on the unused part of the stack by checking that the return capability that he received is not "above" the stack capability he received. This check can be avoided if the return capability is passed on the stack as part of the calling convention. Indeed, if the return capability is stored at some address a', Bob knows by property of directed capabilities that Alice can only have kept a copy of the stack capability with read authority at most up to a'. Thus, Bob will not have to clear his stackframe on return. On the other hand, if Bob passes some stack references to Claire as parameters, Claire will not be able to store anything from her own stackframe in them, thus avoiding the issues described in § 2.2. In fact, Bob can take advantage of this property to ensure that Claire only returns safe values. By passing a stack capability rather than a dedicated register as the return value destination, Bob knows that any return value cannot grant read authority over popped stack frames. The calling convention assumes this strategy, and clears all general purpose registers upon return.

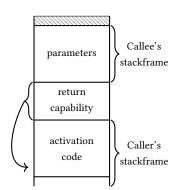

To sum up, our new calling convention is as follows; see also the figure below, which shows what the stack is expected to look like just after a call.

At program start-up. A directed URWLX stack capability is in register  $r_{\rm stk}$ .

When called by an adversary. Check that the received stack capability is a capability of the form (URWLX, DIRECTED, b, e, a), the return capability is expected to be stored at address b.

Before calling an adversary. Push activation record to the stack and create a directed E-capability to use as return capability. Subseg the stack capability to the unused part. Push the return pointer on the stack, as well as all parameters. Clear all registers except  $r_{\rm stk}$  and the program counter before calling.

Before returning to an adversary. Clear all general purpose registers.

Let's consider the cost of one secure call. Our new calling convention does not require any memory clearing, and thus incurs a constant overhead, mainly of clearing registers. Register clearing can be done efficiently using the CClearRegs instruction [Watson et al. 2020]. On the other hand, memory clearing is a costly operation. Previous calling conventions based on LOCAL capabilities all require some amount of stack clearing. Although Georges et al. [2021] improves the situation by only clearing the local stack frame, the calling convention still has an undesired linear cost in the amount of stack memory used.

In summary, we present a faster calling convention, which can realistically be implemented in hardware. Moreover, the calling convention enforces all desired stack safety properties as is proved in the next sections.

#### 3.5 Discussion

While directed capabilities lead to an efficient calling convention, the questions remains whether their new restrictions render them impractical otherwise. Specifically, do directed capabilities hinder critical C idioms, or compiler optimizations to any significant extent. A full investigation of this question is beyond the scope of this paper. However, we conjecture that directed capabilities are sufficiently permissive in practice, and in some cases more practical than, e.g., linear capabilities.

Some objects cannot be allocated on the stack. For instance, a locally allocated circular linked list breaks the directed property. Similarly, any locally allocated node cannot be added to an ambient heap allocated linked list. Indeed, nor should they: stack objects and heap objects often have different lifetimes and are thus generally incompatible.

We do not expect uninitialized capabilities to have major impact on code generation, though one must be careful to initialize an uninitialized object in "increasing" order. Similarly, it takes linear time to allocate and pass stack objects, while C assumes constant time allocation. However, we hasten to point out that it is in general only safe to pass stack objects for which the previous contents cannot be read. [Roessler and DeHon 2018] enforce this efficiently using a lazy tagging and clearing scheme; it would interesting to investigate a similar scheme for uninitialized capabilties.

Furthermore, a compiler must also be careful with the order of stack allocations. Consider for instance the following code snippet:

```

int * x; int y; x = &y;

```

In the above code, the compiler must reorder the allocations for x and y to guarantee the directed property. Such considerations must also be taken into account when implementing compiler optimizations.

All in all, directed capabilities are more restrictive (by design) than local capabilities, but we argue they remain more practical than linear capabilities. For instance, it is a common idiom in C to pass pointers as an argument but not return them to the caller. With linear capabilities, a compiler would need to ensure that all linear capabilities be returned when used in this fashion. Furthermore, some library functions such as

```

int memcmp(const void* p1, const void* p2, size_t size)

```

are not implementable in an linearity-friendly way, since p1 and p2 are allowed to be aliases. We leave a full practical evaluation of directed capabilities to future work.

#### 4 A UNARY MODEL FOR INTEGRITY

In this section, we develop a novel model that captures all the guarantees provided by DIRECTED capabilities and our associated calling convention. The core novelty lies in its ability to express temporal stack safety. The model is made up of two components; a program logic to reason about known and trusted code, and a Kripke logical relation to reason about arbitrary untrusted code. We use the unary model to reason about the *integrity* of example programs.

The program logic is a variant of the one by Georges et al. [2021]; the main change is that some proof rules have been updated to account for directed capabilities, following the operational semantics defined in § 3.1. Thus we refrain from describing the program logic in detail.

Here it suffices to know that the program logic is defined using Iris' weakest preconditions [Jung et al. 2018] (which means that we can re-use the Iris program logic infrastructure to reason formally in Coq) and that the weakest precondition predicate wp Executable  $\{v, Q(v)\}$  intuitively means the program pointed to by the program counter can execute without getting stuck, and that if it terminates, then Q(v) is guaranteed to hold for some final mode v, which can be either Halted or Failed.

Thanks to the dynamic checks of the capability machine, the behaviour of a program is limited by the capabilities it has access to. Thus, even completely arbitrary code must adhere to rules imposed by the capability machine, and will satisfy some notion of *capability safety*. The logical relation captures this notion of capability safety, and serves as a contract between trusted and untrusted code. The fundamental theorem of logical relations (see below) means that any word that is safe to read satisfies that contract. As long as arbitrary code is just a list of instructions (and thus does not,

e.g., include an embedded capability), a corollary then states that even completely arbitrary code satisfies that contract.

Our logical relation is an extension of the one by Georges et al. [2021] and our presentation focuses on the key challenge, which is to extend the model, in particular, the Kripke worlds, to capture the enforcement of temporal properties qua directed capabilities. The execution of a program depends on the physical state of memory. Since we want to reason about stack safety, we are particularly interested in the state of the stack. During execution, different parts of the stack are in different states (e.g. used, unused, etc.). Following Georges et al., we use a Kripke world to model the abstract state of the stack. In essence, the Kripke world is an abstraction of physical memory. Concretely, it tracks which parts are in heap space, which parts are in stack space, and at what particular state a location is. The stack may change in ways that accord with the specific properties we attribute to stack safety. We capture stack-based properties by carefully describing the possible changes to the Kripke world so that they reflect the expected behaviour of the physical stack.

From a technical point of view, a WORLD has two parts:  $W^{std}$  maps addresses to so-called *standard states*, governing *shared* regions, such as the stack; and  $W^{cus}$  maps a countably infinite set of region names to custom state transition systems, governing *owned* regions, such as the private environment of closures.

The logical relation imposes certain invariants on regions of memory that is shared between trusted and untrusted code. Those invariants depend on the state of the stack, and thus on the Kripke world that represents it. We use Iris ghost state to track not only the physical machine state, but also what we call the *instrumented machine state*, which captures the connection between the physical memory, and the abstract state of memory. It uses an Iris predicate called the *standard resource*. A standard resource has two functions: (1) it associates an address of a shared region of memory, in particular each stack address, to its physical state, and (2) it associates that physical state to an invariant. The invariant may depend on the current state of the Kripke world. Our model extends Georges et al. [2021] insofar as it uses the same structure for the instrumented machine state. However, in order to capture temporal properties, we define a *novel* Kripke world, upon which we build new definitions for the standard resources. In this paper, we focus a large part of our attention on the new Kripke world.

In the remainder of this section we first describe the standard states we use to capture stack and heap states, and how these states may evolve, such that they can be used to capture the desired stack properties (§ 4.1). In § 4.2, we will then present the logical relation itself. Finally, we end this section with two examples highlighting what kind of programs we can now verify using our model (§ 4.3).

# 4.1 A New Kripke World

The standard states represent the various states a shared memory address can be in. An address is shared if it lies within the region of authority of a capability that crosses the boundary between known and arbitrary code. The physical state of these addresses will be imposed by invariants, which may in turn depend on the current state of the rest of the machine. For instance, the invariant of a heap region should not be able to depend on the state of the stack and its changes, since locality dictates that the heap is unable to contain stack pointers. Likewise, the invariant of a stack address connected to a lower stack frame will be different from the invariant of the currently live, or popped stack frame. The standard states must therefore also reflect the very specific lifetime properties of a stack frame.

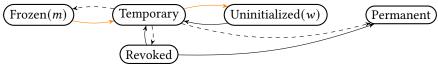

We now explain each of the standard states. The Permanent state represents an allocated heap region. As soon as a heap region is allocated and shared, it becomes permanent. There is no mechanism to free the heap region from its state. The Temporary state represents a live stack

Fig. 6. Standard State Transition System. Full lines indicate public transitions, dashed lines indicate private transitions, orange lines indicate temporal transitions.

frame, i.e., the stack frame owned by the currently executing function. Specifically, it will refer to the *readable* parts of the stack shared between calls. A live stack frame does not need to be Temporary at every step of execution. Rather, the Temporary state is meant to represent the live parts of the stack at the point of change of control. The Uninitialized state represents the unused part of the stack, i.e., a Freed frame or some part of the stack that has never been used. In general, the Uninitialized state will simply refer to the parts of the stack that cannot be read from, only written to. The Frozen(m) state represents a frozen stack frame, i.e., the parts of a frame not shared with a new callee. Here m maps the addresses of that particular frame to their frozen values. The Revoked state represents a part of the stack which is currently owned by an executing function. A region is not part of the shared stack while it is Revoked.

Next we define how a standard state may evolve in order to reflect physical stack changes that accord with the key properties of stack safety (LSE, WBCF, and temporal stack safety). Some stack changes are not observable by any caller or callee, whereas other changes are public and observable by both. As long as temporal stack safety is enforced, some stack changes (such as popping a stack frame) are safe to observe by the caller, but not by higher stack frames. After all, it is not safe to pop a frame if there are still live frames on top of it.

We use three kinds of transitions to reflect these distinctions. A transition is *observable* whenever some entity is oblivious to that transformation. Public transitions (depicted in Fig. 6 as straight black lines) are those that are observable by all functions. Private transitions (dashed lines) can only be observed by the currently executing function. Finally, temporal transitions (orange lines) are only observable by functions that are still present on the call stack.

Using these transitions, we isolate three future world relations. A world W' is a public future world of W,  $W' \supseteq^{pub} W$ , if all the states in W' are either connected to a fresh address or region name, or were updated from W through public transitions only. A private future world  $W' \supseteq^{priv} W$  allows for public, temporal or private transitions. Finally, the third relation we consider is in fact a family of future world relations, where each relation is indexed by an address. We say that W' is a future world of W relative to address a, written as  $W' \supseteq^a W$ , when the state of all addresses *below* a were updated via public transitions only, while addresses at or above a were updated via public or temporal transitions.

For instance, consider an address a' that is Temporary in W. If that address lies below a, it must still be Temporary in W' if  $W' \supseteq a$  W. However, if that address lies at or above a, it may change to an uninitialized state. Likewise, any address at or above a with an Uninitialized(w) state in W may change to a new Uninitialized(w') state.

A relative future world relation captures the changes to a stack *relative* to a specific stack frame (delimited by its upper bound address). From the point of view of a particular stack frame, a new call will push then pop new stack frames, whereas that stack frame *remains* frozen or initialized. Upon return of a well-bracketed call, a stack frame is safe to pop. In other words, invoking a return capability should be safe to do in a world where the current as well as all higher stack frames are uninitialized. In  $W' \supseteq^a W$ , world W' represents such a world, from the perspective of a stack frame with upper bound a.

The instrumented machine state imposes monotonicity requirements on the invariants associated with shared addresses<sup>4</sup>. If a shared address a is part of the heap, then the associated invariant must be monotone with regards to  $\exists^{priv}$ . On the other hand, if a is part of the (live) stack, then the associated invariant must be monotone with regards to  $\exists^a$ .

We finish this section by highlighting some interesting transitions, relating them to the corresponding physical state changes of the stack:

- Temporary ---→ Frozen(m): local variables freeze when their associated function makes a new call. These local variables are stored in a stack frame. The frozen part of a stack frame cannot be written to while it is frozen. A stack frame cannot stay frozen forever. In particular, a frozen stack frame must thaw when control is returned to its caller. A caller should therefore not be able to observe that the stack frame was at any point frozen during execution, hence the private transition.

- Frozen(*m*) Temporary: as indicated in the previous point, a frozen stack frame must thaw before it can be written to again. A frozen stack frame is thawed only after a callee invokes the callback. Temporal stack safety dictates that only higher stack frames can invoke the callback. Invoking the callback effectively pops the callee's stack frame. Thus a local stack frame is thawed once all higher stack frames have been popped, but has no effect on lower stack frames.

- Temporary Uninitialized(w): Finally, local stack frames are popped upon return. Thanks to temporal stack safety, popping a stack frame has no effect on lower stack frames, since they cannot read its content.

In summary, we have presented the standard states and transitions that make up the new Kripke world used to model LSE, WBCF and now also temporal stack safety. The world differs from [Georges et al. 2021] in the following way: we distinguish between the Uninitialized state (shared write access but no shared read access) and the Frozen state (no shared write or read access), and we introduce a new kind of transition for defining a relative future world relation, capturing the temporal properties of the stack.

# 4.2 A Unary Logical Relation

Fig. 7 defines the unary Kripke logical relation with support for temporal stack safety. We depict in blue the parts of the definition that are different from the unary logical relation used by Georges et al. [2021].

The value relation  $\mathcal{V}: \mathsf{WORLD} \to \mathsf{Word} \to \mathit{iProp}$  defines the validity of a word relative to a world; the register relation  $\mathcal{R}$  defines the validity of a register state; and the expression relation  $\mathcal{E}$  defines when it is safe to use a word as the program counter. Note that all relations are defined in the Iris program logic (cf. the type  $\mathit{iProp}$  for Iris propositions). We now explain the definition, and first consider the value relation. Integers and words with 0 capability are always valid. A word with a read and/or write permission is valid in a world  $\mathit{W}$  only if certain conditions on  $\mathit{W}$  are met. A Global capability with a read and/or write permission imposes a Permanent state on its range of authority. An uninitialized capability with a write-local (i.e., it can be used to store local and directed words) permission imposes a Temporary state on its initialized readable range of authority, whereas its uninitialized part may be either Temporary or Uninitialized. The state relations  $\mathit{S}$  and  $\mathit{S}^{\mathit{u}}$  define the exact conditions on  $\mathit{W}$  for regular and uninitialized capabilities respectively.

A valid capability with read and/or write permission grants access to the so-called standard resources alluded to in the beginning of this section:  $rel(a, \phi)$  associates the memory predicate  $\phi : WORLD \rightarrow Word \rightarrow iProp$  to the address a. It suffices to think of  $rel(a, \phi)$  as an invariant, that

$<sup>^4</sup>$ The formal definitions of the instrumented machine state and standard resources are here omitted for brevity, full definitions can be found in the Coq formalisation.

Fig. 7. A Logical Relation with Support for Temporal Stack Safety.  $\supseteq^g$  equals  $\supseteq^{priv}$  whenever g is GLOBAL or LOCAL, and  $\supseteq^e$  whenever g is DIRECTED

can be used to access the ghost state of a, while guaranteeing that  $\phi$  holds at the current physical state of a in the current world W. Normally, the predicate we associate with such an address a would be  $\mathcal V$  itself. However, we distinguish between a read-only and a read-write permission by allowing the associated predicate of an address within a read-only region to be stronger than  $\mathcal V$ . The predicate in question then needs to satisfy the read condition  $\mathrm{rcond}(\phi)$ , which imposes two restrictions on  $\phi$ . First, it enforces that  $\phi(W)(w)$  always implies validity, regardless of W and w. Second, it enforces that  $\phi(W)(w)$  never depends on W when w is an integer. In other words, only capabilities can depend on the instrumented machine state. Notice how each condition is guarded by a later (>) modality; this is to guarantee that the definition of  $\mathcal V$  is well defined (here we use that Iris supports the definition of guarded recursive predicates).

An E capability can only be jumped to, hence its validity is defined in terms of its safe execution. Such a capability can be jumped to at any moment and hence the property should be persistent (i.e., not rely on any ephemeral resources); this is expressed by Iris' persistence modality  $\square$ . The execution of a capability may depend on the current state of the stack. For instance, a Global E capability represents a global function closure, and is safe to jump to regardless of the state of the stack. On the other hand, a directed closure (used for return pointers) is only safe to jump to at the end of a function's execution. This distinction is made by quantifying over the possible future worlds an E capability may be invoked from, see  $W' \supseteq^g W$ . A Global of local closure can be invoked in any private future world of W, whereas a directed closure can only be invoked in a

relative future world  $W' \supseteq^e W$ , where e will represent the upper bound of the stack frame being returned to.

Finally, the safe execution of a word is defined using the expression relation  $\mathcal{E}$ . The expression relation is defined in terms of the program logic that the logical relation is built upon. Specifically,  $\mathcal{E}(W)(w)$  expresses that given an instrumented machine state beginning at world W, and a safe register state  $\mathcal{R}(r)$ , the word w is safe to execute. That is, the weakest precondition holds for a configuration in which the pc contains w, with a post condition that enforces the instrumented machine state, i.e., all the established invariants hold at some private future world.

Now that we have our definition of the logical relation in place, we can state the fundamental theorem of logical relations. We refer to the Coq mechanisation for its full proof, and the technical report [Georges et al. 2022, Appendix A] for a proof sketch.

THEOREM 4.1 (FTLR). Assume that p = RX, p = RWX or  $(p = RWLX \land g = DIRECTED)$ . Assume also that V(W)(p, g, b, e, a). Then we have that  $\mathcal{E}(W)(p, g, b, e, a)$ .

#### 4.3 Examples

We show how to use the unary model to prove safety of two example programs: Listings 7 and 9 in capability machine code. These two examples illustrate two properties that have not been explored in previous formalizations. Each program uses an assert subroutine that tests the integrity of encapsulated state. Although we will not present it in this paper, we have also proved the safety of the awkward example (Lis. 5), which can be found in the Coq mechanization.

4.3.1 Protection against Dangling Stack Pointers. Fig. 8 depicts a program with an assertion whose success depends on the absence of dangling stack pointers. g1 creates a closure around some code f1 and a dynamically allocated location containing the integer 2. The macro crtcls  $[r_2]$   $r_3$  allocates a closure where  $r_3$  points to the closure's code (created using the *offset* from g1 to f1), and  $r_2$  points to the newly allocated environment; the resulting closure is an enter capability.

```

(closure creation around f1)

g1: malloc r_2

store r_2 2

move r_3 pc

lea r_3 offset

crtcls [r_2] r_3

jmp r_0

f1: prepstack r_{

m stk}

loadU r_0 r_{\rm stk} (-1)

(intentional leak)

push r_{\rm env}

load r_{

m env} r_{

m env}

(integrity assertion)

assert r_{\rm env} 2

rclear RegName\{pc, r_0}

jmp r_0

```

f1 applies the calling convention from § 3.4: (1) it prepares the stack by checking that the stack has permission URWLX and lowers its address to point to the bottom of its bound, and (2) it loads the return capability parameter which has been passed on the stack itself. Now the idea is that since the parameter was stored on the stack, it must either be a heap closure, or a stack allocated activation record of an *older* stack frame qua temporal stack safety. Thus, when f1 attempts to leak the private capability of the closure by pushing a copy of the private capability onto the stack, temporal stack safety ought to ensure that the content of the stack frame cannot be read once popped and thus that the leaked capability remains inaccessible from the environment after we return from f1. Finally, f1 clears the registers and returns to the caller by invoking the return capability that was passed on the stack. Note that f1's stack frame is *not* cleared.

Fig. 8. Assembly of Lis. 7 Recall that f1's assertion hinges on the fact that any caller to the closure created by g1 is not able to read the popped stack frame (§ 2.2.1). We use the unary model to prove that within any arbitrary context of a certain layout, the assertion flag associated with the assert subroutine stays at 0 at every step of the execution, meaning that the assertion never fails.

```

Theorem 4.2. (Correctness of the temporal stack safety example) Let reg \in Reg, m \in Mem and c_{temp} \triangleq (RX, GLOBAL, ...) c_{stk} \triangleq (URWLX, DIRECTED, ...) c_{adv} \triangleq (RWX, GLOBAL, ...)

```

where the capabilities have an appropriate range of authority and pointer. Furthermore, assume that:

- m has been initialized with the code of the program and subroutines (pointed to by  $c_{temp}$ ), an uninitialized stack (pointed to by  $c_{stk}$ ), and unknown adversarial code (pointed to by  $c_{adv}$ );

- $reg(pc) = c_{temp}$ ,  $reg(r_{stk}) = c_{stk}$ ,  $reg(r_0) = c_{adv}$  and  $reg(r) \in \mathbb{Z}$  otherwise;

- flag denotes the assertion flag, initialized to 0;

```

If (Executable, (reg, m)) \rightarrow^* (\mu, (reg', m')) then m'(flag) = 0.

```

PROOF. We prove this statement in two stages. First, we show that g1 is safe according to the expression relation in any world W;  $\mathcal{E}(W)(E, GLOBAL, b_{temp}, e_{temp}, g1)$ . Next, we conclude by applying the adequacy of weakest preconditions.