Sander Huyghebaert

Steven Keuchel

Coen De Roover

Dominique Devriese

## Outline

Introduction

**Universal Contracts**

MinimalCaps

RISC-V PMP

Conclusion

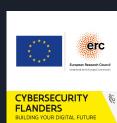

### Introduction

#### Traditionally:

- Long manuals

- Prose/Pseudocode

#### Recently:

- Formal & executable spec

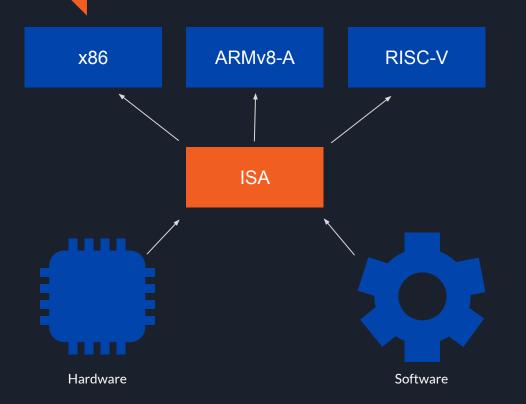

### Sail

### Security Guarantees

Example: AMD64

"Only privileged software running at CPL=0 can manage the TLBs."

"Page translation is controlled by the PG bit in CR0 (bit 31). When CR0.PG is set to 1, page translation is enabled."

"Most instructions used to access these resources are privileged and can only be executed while the processor is running at CPL=0, although some instructions can be executed at any privilege level."

- AMD64 Architecture Programmer's Manual Volume 2: System Programming

- Informal ISA specs offer *promise* of security guarantee

- "Security feature X offers Y / prevents attack Z"

- Holds for future updates to the ISA

- Formal ISA specs *lack* security specifications

- Focus is on operational specification

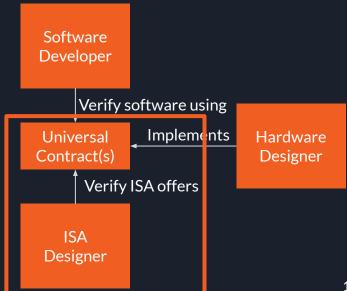

## Universal Contracts Motivation

- Security guarantees should be

- Part of ISA specification

- Formal

- Verifiable against operational spec

- Specific enough for reasoning

- Not overspecified

- Optimizations and extensions should be possible

- Mechanized

- Current approaches do *not* meet these requirements

# Universal Contracts Concept

{P}ASM code {Q}

- Formal security guarantee...

- ... expressed as a contract

- Upper bound of the authority

- Holds for any code

- Verifiable against operational specification of ISA

- Sail

- Fetch-Decode-Execute Cycle

# Universal Contracts Concept

{P}ASM code {Q}

- Formal security guarantee...

- ... expressed as a contract

- Upper bound of the authority

- Holds for any code

- Verifiable against operational specification of ISA

- Sail

- Fetch-Decode-Execute Cycle

# Universal Contracts Concept

{P}ASM code {Q}

- Formal security guarantee...

- ... expressed as a contract

- Upper bound of the authority

- Holds for any code

- Verifiable against operational specification of ISA

- Sail

- Fetch-Decode-Execute Cycle

## Outline

Introduction

Universal Contracts

MinimalCaps

RISC-V PMP

Conclusion

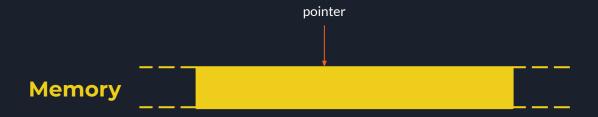

## Traditional Machine

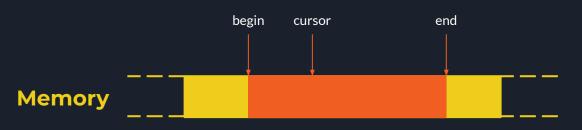

## The MinimalCaps Capability Machine

### **Capability**

- perm  $\subseteq$  {O, E, R, RW}

- cursor:address

- begin : address

- end :address

## The MinimalCaps Capability Machine

### **Capability**

- perm  $\subseteq$  {O, E, R, RW}

- cursor : address

- begin : address

- end : address

### **Hardware Guarantees**

- Capabilities are unforgeable

- Permissions are checked

- Capability manipulation is safe

## Capability Safety Universal Contract

```

{(\exists c, pc \mapsto c * \mathcal{V}(c) * CorrectPC(c)) * (*_{r \in GPR} \exists w. r \mapsto w * \mathcal{V}(w))} fdeCycle {T}

```

#### Value Relation $\mathcal{V}$ : (Integer + Capability) -> iProp

$$\mathcal{V}(w) \begin{cases} \mathcal{V}(z), \mathcal{V}(O, -, -, -) = \text{True } (z \text{ is an integer}) \\ \mathcal{V}(E, b, e, a) &= \triangleright \square \, \mathbf{E}(R, b, e, a) \\ \mathcal{V}(R, b, e, -) &= \bigstar_{a \in [b, e]} \, \frac{\exists \, w, a \mapsto w \, \bigstar \, \mathcal{V}(w)}{\exists \, w, a \mapsto w \, \bigstar \, \mathcal{V}(w)} \\ \mathcal{V}(RW, b, e, -) &= \bigstar_{a \in [b, e]} \, \frac{\exists \, w, a \mapsto w \, \bigstar \, \mathcal{V}(w)}{\exists \, w, a \mapsto w \, \bigstar \, \mathcal{V}(w)} \end{cases}$$

$$\epsilon(w) = (pc \mapsto w * (*_{r \in GPR} \exists w. r \mapsto w * \mathcal{V}(w))) -*$$

wp fdeCycle T

#### Value Relation $\mathcal{V}$ : (Integer + Capability) -> iProp

$$\mathcal{V}(w) \begin{cases} \mathcal{V}(z), \mathcal{V}(O, -, -, -) = \text{True } (z \text{ is an integer}) \\ \mathcal{V}(E, b, e, a) &= \triangleright \square \ \mathcal{E}(R, b, e, a) \\ \mathcal{V}(R, b, e, -) &= \ *_{a \in [b, e]} \ \exists \ w, a \mapsto w \ * \ \mathcal{V}(w) \\ \mathcal{V}(RW, b, e, -) &= \ *_{a \in [b, e]} \ \exists \ w, a \mapsto w \ * \ \mathcal{V}(w) \end{cases}$$

$$\mathbf{\epsilon}(\mathbf{w}) = (\mathbf{pc} \mapsto \mathbf{w} * (\mathbf{*}_{r \in GPR} \exists \mathbf{w}. r \mapsto \mathbf{w} * \mathcal{V}(\mathbf{w}))) - *$$

wp fdeCycle T

#### Value Relation $\mathcal{V}$ : (Integer + Capability) -> iProp

$$\mathcal{V}(w) \begin{cases} \mathcal{V}(z), \mathcal{V}(0, -, -, -) = \text{True } (z \text{ is an integer}) \\ \mathcal{V}(E, b, e, a) &= \triangleright \square \mathcal{E}(R, b, e, a) \\ \mathcal{V}(R, b, e, -) &= \bigstar_{a \in [b, e]} \exists w, a \mapsto w \bigstar \mathcal{V}(w) \\ \mathcal{V}(RW, b, e, -) &= \bigstar_{a \in [b, e]} \exists w, a \mapsto w \bigstar \mathcal{V}(w) \end{cases}$$

Invariants

$$\mathbf{\varepsilon}(\mathbf{w}) = (\mathsf{pc} \mapsto \mathsf{w} * (*_{\mathsf{r} \in \mathsf{GPR}} \exists \mathsf{w}. \mathsf{r} \mapsto \mathsf{w} * \mathcal{V}(\mathsf{w}))) - *$$

wp fdeCycle T

#### Value Relation $\mathcal{V}$ : (Integer + Capability) -> iProp

$$\mathcal{V}(w) \begin{cases} \mathcal{V}(z), \mathcal{V}(0, -, -, -) = \text{True } (z \text{ is an integer}) \\ \mathcal{V}(E, b, e, a) &= \triangleright \square \mathbf{E}(R, b, e, a) \\ \mathcal{V}(R, b, e, -) &= \bigstar_{a \in [b, a]} \exists w, a \mapsto w * \mathcal{V}(w) \\ \mathcal{V}(RW, b, e, -) &= \bigstar_{a \in [b, a]} \exists w, a \mapsto w * \mathcal{V}(w) \end{cases}$$

$$\epsilon(w) = (pc \mapsto w * (*_{r \in GPR} \exists w. r \mapsto w * \mathcal{V}(w))) -*$$

wp fdeCycle T

# Capability Safety Step Contract

```

{ (\exists c, pc \mapsto c * \mathcal{V}(c) * CorrectPC(c)) * (\bigstar_{r \in GPR} \exists w. r \mapsto w * \mathcal{V}(w)) } step

{ (\exists c, pc \mapsto c * (\mathcal{V}(c) \forall \epsilon(c))) * (\bigstar_{r \in GPR} \exists w. r \mapsto w * \mathcal{V}(w)) }

```

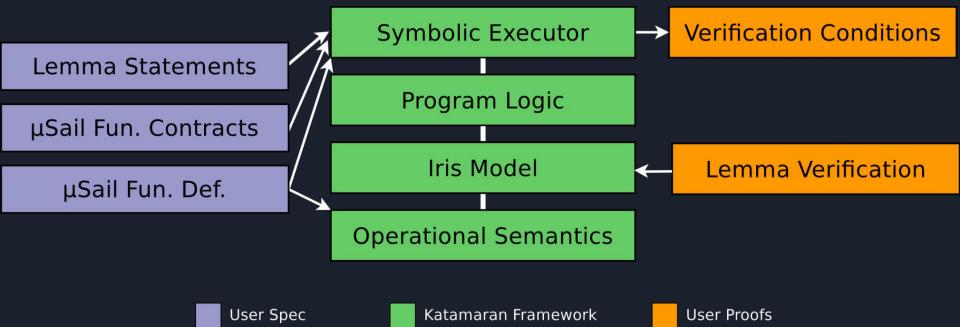

## Katamaran

Semi-automatic separation logic verifier

Verified Symbolic Execution with Kripke Specification Monads (and No Meta-programming)

STEVEN KEUCHEL, Vrije Universiteit Brussel, Belgium SANDER HUYGHEBAERT, Vrije Universiteit Brussel, Belgium GEORGY LUKYANOV, Newcastle University, United Kingdom DOMINIQUE DEVRIESE, KU Leuven, Belgium

```

{ (\exists c, pc \mapsto c \bigstar \mathcal{V}(c) \bigstar CorrectPC(c)) \bigstar (\bigstar<sub>r \in GPR</sub> \exists w. r \mapsto w \bigstar \mathcal{V}(w)) }

function exec sd(rs : GPR, rb : GPR, immediate : int) : bool :=

let base cap := call read reg cap rb in

let (perm, beg, end, cursor) := base cap in

let c := (perm, beg, end, cursor + immediate) in

let b := call write allowed perm in

assert b ;;

let w := call read_reg rs in

use lemma (subperm not E RW perm);;

use lemma (move cursor base cap c) ;;

call write mem c w ;;

call update pc ;; true

\{ (\exists c, pc \mapsto c * (\mathcal{V}(c) \lor \epsilon(c))) * (*_{r \in GPR} \exists w. r \mapsto w * \mathcal{V}(w)) \}

```

```

{ (\exists c, pc \mapsto c \bigstar \mathcal{V}(c) \bigstar CorrectPC(c)) \bigstar (\bigstar<sub>r \in GPR</sub> \exists w. r \mapsto w \bigstar \mathcal{V}(w)) }

function exec sd(rs : GPR, rb : GPR, immediate : int) : bool :=

assert b ::

{ rb \mapsto base_cap * \mathcal{V}(base_cap) * rs \mapsto w * \mathcal{V}(w) ...}

use lemma (subperm not E RW perm);;

{ rb \mapsto base_cap * \mathcal{V}(base_cap) * rs \mapsto w * \mathcal{V}(w) * perm \neq E ...}

use lemma (move cursor base cap c) ;;

call write mem c w ;;

call update pc ;; true

\{ (\exists c, pc \mapsto c * (\mathcal{V}(c) \lor \epsilon(c))) * (*_{r \in GPR} \exists w. r \mapsto w * \mathcal{V}(w)) \}

```

```

{ (\exists c, pc \mapsto c \star \mathcal{V}(c) \star CorrectPC(c)) \star (\star<sub>r \in GPR</sub> \exists w. r \mapsto w \star \mathcal{V}(w)) }

function exec sd(rs : GPR, rb : GPR, immediate : int) : bool :=

assert b ::

{ rb \mapsto base_cap * \mathcal{V}(base_cap) * rs \mapsto w * \mathcal{V}(w) ...}

use lemma (subperm not E RW perm) ;;

use lemma (move cursor base cap c) ;;

{ rb \mapsto base_cap * \mathcal{V}(base_cap) * rs \mapsto w * \mathcal{V}(w) * \mathcal{V}(c) ...}

call write mem c w ;;

call update pc ;; true

\{ (\exists c, pc \mapsto c * (\mathcal{V}(c) \lor \epsilon(c))) * (*_{r \in GPR} \exists w. r \mapsto w * \mathcal{V}(w)) \}

```

```

{ (\exists c, pc \mapsto c * \mathcal{V}(c) * CorrectPC(c)) * (*_{r \in GPR} \exists w. r \mapsto w * \mathcal{V}(w))}

function exec sd(rs : GPR, rb : GPR, immediate : int) : bool :=

{ rb \mapsto base_cap * \mathcal{V}(base_cap) * rs \mapsto w * \mathcal{V}(w) ...}

use lemma (subperm not E RW perm) ;;

use lemma (move cursor base cap c) ;;

{ rb \mapsto base_cap * \mathcal{V}(base_cap) * rs \mapsto w * \mathcal{V}(w) * \mathcal{V}(c) ...}

call write mem c w ;;

call update pc ;; true

\{ (\exists c, pc \mapsto c * (\mathcal{V}(c) \lor \epsilon(c))) * (*_{r \in GPR} \exists w. r \mapsto w * \mathcal{V}(w)) \}

```

```

{ (\exists c, pc \mapsto c \bigstar \mathcal{V}(c) \bigstar CorrectPC(c)) \bigstar (\bigstar<sub>r \in GPR</sub> \exists w. r \mapsto w \bigstar \mathcal{V}(w)) }

function exec sd(rs : GPR, rb : GPR, immediate : int) : bool :=

assert b ::

{ rb \mapsto base_cap * \mathcal{V}(base_cap) * rs \mapsto w * \mathcal{V}(w) ...}

use lemma (subperm not E RW perm) ;;

use lemma (move cursor base cap c) ;;

{ rb \mapsto base_cap * \mathcal{V}(base_cap) * rs \mapsto w * \mathcal{V}(w) * \mathcal{V}(c) ...}

call write_mem c w ;;

call update_pc ;; true

\{ (\exists c, pc \mapsto c * (\mathcal{V}(c) \lor \epsilon(c))) * (*_{r \in GPR} \exists w. r \mapsto w * \mathcal{V}(w)) \}

```

### RISC-V

- Free, open, extensible ISA

- 32-bit instructions

- We focus on RV32I

- Official RISC-V spec

- But with PMP support

- U and M modes

- Simplifications

- Limited PMP entries

| Extension | Description                         |  |  |

|-----------|-------------------------------------|--|--|

| 1         | Integer                             |  |  |

| M         | Integer Multiplication and Division |  |  |

| A         | Atomics                             |  |  |

| F         | Single-Precision Floating Point     |  |  |

| D         | Double-Precision Floating Point     |  |  |

| С         | 16-bit Compressed Instructions      |  |  |

| Xext      | Non-Standard User-Level Extension   |  |  |

G

## RISC-V PMP Physical Memory Protection

- Optional

- Grant permissions to S and U modes

- By default none

- Revoke permissions from M mode

- By default full

- PMP violations => trap

- Load access fault, store access fault, ...

- Exception

- Up to 64 PMP regions

- Statically prioritized

- Lowest number has highest priority

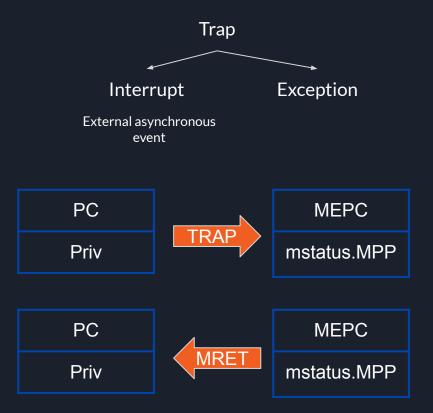

Trap

Interrupt Exception

External asynchronous event

- Optional

- Grant permissions to S and U modes

- By default none

- Revoke permissions from M mode

- By default full

- PMP violations => trap

- Load access fault, store access fault, ...

- Exception

- Up to 64 PMP regions

- Statically prioritized

- Lowest number has highest priority

## RISC-V PMP Physical Memory Protection

- Optional

- Grant permissions to S and U modes

- By default none

- Revoke permissions from M mode

- By default full

- PMP violations => trap

- Load access fault, store access fault, ...

- Exception

- Up to 64 PMP regions

- Statically prioritized

- Lowest number has highest priority

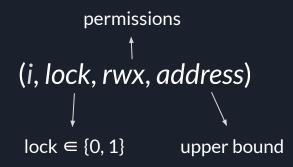

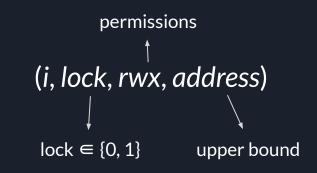

# RISC-V PMP PMP Entry

# RISC-V PMP PMP Entry

Bounds  $PMP_i = [address_{i-1}, \overline{address_i})$

### RISC-V PMP

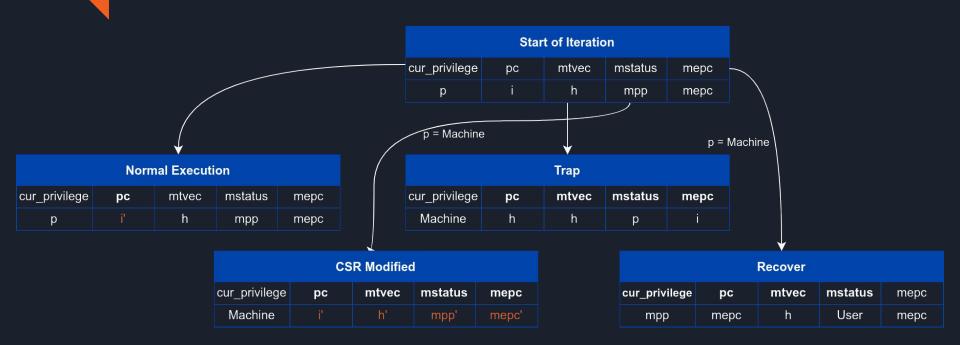

**State Transition: Trap**

| Start of Iteration |    |       |         |      |  |  |

|--------------------|----|-------|---------|------|--|--|

| cur_privilege      | рс | mtvec | mstatus | mepc |  |  |

| р                  | i  | h     | mpp     | mepc |  |  |

|                    |    |       |         |      |  |  |

| Trap               |    |       |         |      |  |  |

| cur_privilege      | рс | mtvec | mstatus | mepc |  |  |

| Machine            | h  | h     | р       | i    |  |  |

## RISC-V PMP State Transition

# RISC-V PMP Universal Contract

```

{ Start

* ▷ (CSRMod -* wp fdeCycle T)

* ▷ (Trap -* wp fdeCycle T)

* ▷ (Recover -* wp fdeCycle T) }

fdeCycle

{T}

```

# RISC-V PMP Universal Contract

```

{ Start

* ▷ (CSRMod -* wp fdeCycle T)

* ▷ (Trap -* wp fdeCycle T)

* ▷ (Recover -* wp fdeCycle T) }

fdeCycle

{T}

```

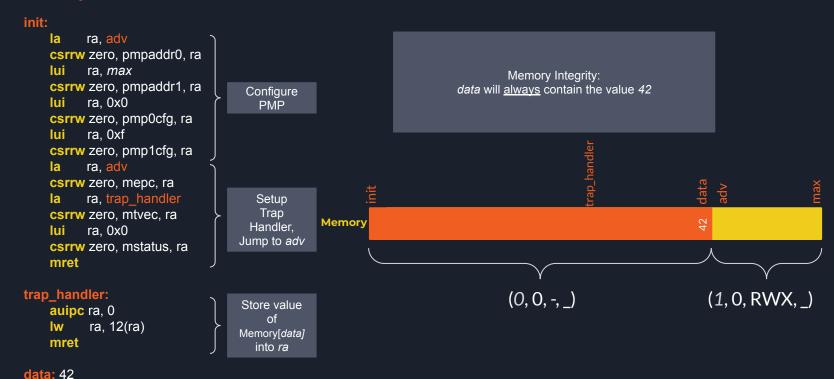

## **Full-System Proof: FemtoKernel**

```

Memory Integrity:

data will always contain the value 42

Approximately the property of the pr

```

## **Full-System Proof: FemtoKernel**

```

init:

ra, adv

csrrw zero, pmpaddr0, ra

ra, max

Memory Integrity:

csrrw zero, pmpaddr1, ra

data will always contain the value 42

Configure

lui ra, 0x0

PMP

csrrw zero, pmp0cfg, ra

lui ra, 0xf

csrrw zero, pmp1cfg, ra

Memory

(0, 0, -, \_)

```

(1, 0, RWX, \_)

## **Full-System Proof: FemtoKernel**

```

init:

ra, adv

csrrw zero, pmpaddr0, ra

ra, max

Memory Integrity:

csrrw zero, pmpaddr1, ra

data will always contain the value 42

Configure

ra, 0x0

PMP

csrrw zero, pmp0cfg, ra

lui

ra, 0xf

csrrw zero, pmp1cfg, ra

ra, adv

csrrw zero, mepc, ra

ra, trap_handler

Setup

Trap

csrrw zero, mtvec, ra

Memory

Handler.

ra, 0x0

Jump to adv

csrrw zero, mstatus, ra

mret

(1, 0, RWX, _)

(0, 0, -, \_)

```

adv: ...

## **Full-System Proof: FemtoKernel**

42

## Conclusion

- Comparison with Cerise

- Proof effort reduction

- Not entirely fair

- Added Instruction

- Uninteresting case

- o RISC-V PMP: +2 LoC

- MinimalCaps: +23 LoC

- FemtoKernel

|     | MinimalCaps | RISC-V PMP | Cerise |

|-----|-------------|------------|--------|

| LoC | 2867        | 3880       | 7919   |

## Summary

- Security Guarantees

- Formalized as Universal Contracts

- Part of security specification

- Verified against operational specification

- Case Study: MinimalCaps

- Capability safety

- Case Study: RISC-V PMP

- Memory Integrity

- Katamaran

- Semi-automatic separation logic verifier

# Side-channels Future Work

- Current focus on *integrity* guarantees

- Software observable side-channels

- Timing-based side-channels (Instruction Timing)

- Should be part of security specification

- ISA should not specify all details...

- ... but enough to reason about it

### Cerise: Program Verification on a Capability Machine in the Presence of Untrusted Code

AÎNA LINN GEORGES, Aurhus University, Denmark ARMAEL GUËNEAU, Aarhus University, Denmark THOMAS VAN STRYDONCK, KU Leuven, Belgium AMIN TIMANY, Aarhus University, Denmark ALIX TRIEU, Aarhus University, Denmark DOMINIQUE DEVRIESE, Vrije Universiteit Brussel, Belgium LARS BIRKEDAL, Aarhus University, Denmark

A capability machine is a type of CPU allowing fine-grained privilege separation using capabilities, machine words that represent certain kinds of authority. We present a mathematical model and accompanying proof methods that can be used for formal verification of functional correctness of programs running on a capability machine, even when they invoke and are invoked by unknown (and possibly malicious) code. We use program logic called Cerise for reasoning about known code, and an associated logical relation, for reasoning about known code. And an associated logical relation, for reasoning about known code. The logical relation formally countries the capability machine. The Cerise program logic, logical relation, and all the examples considered in the paper have been mechanized using the list program logic, logical relation, and all the examples considered in the paper have been mechanized using the list program logic, framework in the Cop proof assistant.

The methodology we present underlies recent work of the authors on formal reasoning about capability machines [Georges et al. 2021; Skorstengaard et al. 2019s; Van Strytonke et al. 2021], but was left somewhat implicit in those publications. In this paper we present a pedagogical introduction to the methodology, in a simpler setting (no exotic capabilities), and starting from minimal examples. We work our way up to new results about a heap-based calling convention and implementations of sophisticated object-capability patterns of the kind previously studied for high-level languages with object-capabilities, demonstrating that the methodology scales to such reasoning.

#### ACM Reference Format:

Aïna Linn Georges, Armaël Guéneau, Thomas Van Strydonck, Amin Timany, Alix Tricu, Dominique Devriese, and Lars Birkedal. 2021. Cerise: Program Verification on a Capability Machine in the Presence of Untrusted Code, J. ACM, 1, 1 (October 2021), 55 pages. https://doi.org/10.1145/mnnnnn.nnnnnn

#### 1 INTRODUCTION

A capability machine is a type of CPU that enables fine-grained memory compartmentalization and privilege separation through the use of capabilities. This type of hardware architecture has been studied since the 60ies [Dennis and Van Horn 1966; Levy 1984], and in particular more recently as part of the CHERI project [Watson et al. 2020]. Capability machines offer fine-grained and scalable

Authors' addresses. Aina Linn Georges, ageorges@cs.au.dk, Aarhus University. Denmark: Armael Guéneau, armael@cs.au.dk,

Aarhus University, Denmark; Thomas Van Strydonck, thomas vanstrydonck@cs.kuleuvenbe, KULeuven, Belgum, Anim

Timany, timany@cs.au.dk, Aarhus University, Denmark; Alix Tireu, alixtrieu@cs.au.dk, Aarhus University, Denmark;

Dominique Devriese, dominique devriese@vub.be, Vrije Universitiet Brussel, Belgium; Lars Birkedal, birkedal@cs.au.dk,

Aarhus University, Denmark;

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies have this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to relistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

© 2021 Association for Computing Machinery.

0004-5411/2021/10-ART \$15.00

https://doi.org/10.1145/nnnnnnnnnnnnnnn

J. ACM, Vol. 1, No. 1, Article . Publication date: October 2021.

### Verified security for the Morello capability-enhanced prototype Arm architecture

THOMAS BAUEREISS, University of Cambridge, UK BRAN CAMPBELL, University of Edinburgh, UK THOMAS SEWELL, University of Edinburgh, UK ALASDAM RAMSTROW, University of Cambridge, UK ALASDAM RAMSTROW, University of Cambridge, UK IAN STARK, University of Edinburgh, UK GRAEM BARNES, Am Ld, UK ROBERT N. M. WATSON, University of Cambridge, UK PETER SEWELL University of Cambridge, UK PETER SEWELL UNIVERSITY OF CAMBRIDGE, UK ROBERT N. M. WATSON, University of Cambridge, UK

Memory safety bugs continue to be a major source of security vulnerabilities in our critical infrastructure. The CHERI project has proposed extending conventional architectures with hardware-supported capabilities to enable fine-grained memory protection and scalable compartmentalisation, allowing historically memory-unsafe. C and C++ to be adapted to deterministically mitigate large classes of vulnerabilities, while requiring only mitigate large classes of vulnerabilities, while requiring soft purior changes to existing system software sources. Arm is currently designing and building Morello. a CHERI enabled prototype architecture, processor, Scé., and board, extending the high-performance Noveree N1, to enable industrial evaluation of CHERI and pare the way for potential board, continued to the processor of the protection in timeda to, and that cannot be done with conventional engineering the changes of the protection in timeda to, and that cannot be done with conventional engineering

In this paper we put the Morello architecture on a solid mathematical footing from the outset. We define the fundamental security property that Morello aims to provide, reachable equality monotronicity, and prove that the architecture definition satisfies it. This proof is mechanised in Isabelle/HOL, and applies to a translation of the official Arm Morello specification into Isabelle. The main challenge is handling the complexity and suck of a production achietcure (2600 lines of Isabelle. We do so by factoring the proof when architecture (2600 lines of Isabelle. We do so by factoring the proof when a narrow abstraction capturing the escential properties of instruction execution in an arbitracy CHEMI EA, express adors a normal interinstruction remaintee. We also develop a financial result of the complexity of the control of the complexity of the

This gives us machine-checked mathematical proofs of whole-ISA security properties of a full-scale industry architecture, at design-time. To the best of our knowledge, this is the first demonstration that that is feasible, and it significantly increases confidence in Morello.

### 1 INTRODUCTION

#### 1.1 The CHERI and Morello Context

Memory safety bugs continue to be a major source of security vulnerabilities, responsible for around 70% of those addressed by Microsoft security updates, and around 70% of the high-severity bugs impacting Chronium [28, 42]. Their root causes are well-known legacy design choices and limitations of normal practice; pervasive uses of systems programming languages that do not enforce memory protection, hardware that enforces only coarse-grain protection, with vitual memory, and lest-and-febug development methods that cannot provide high assurance. These are baked in to the critical systems codebase across the industry, and the result, in today's adversarial environment, is that programming errors can often lead to exploitable vulnerabilities.

There are many possible approaches to improving this situation, including development of safer programming languages, techniques for full functional-correctness verification, and better bug-finding tools. Each is the subject of much research in programming languages and semantics, and all are worthwhile, but the legacy investment, the need for systems code to work close to the machine, and the inability of bug-finding to provide high assurance, makes it were hard to radically improve masses-market vastems.

Another path, less well explored, is to change the architectural interface to provide hardware mechanisms that enable better enforcement of memory protection. Over the last ten years, the CHERI project [1] has been extending conventional hardware instruction-Set Architectures (ISAs) with new architectural features to enable fine-grained memory protection and highly scalable software compartmentalisation. The CHERI memory-protection features allow historically memory-unsafe programming languages each as C and C++ to be adapted to have quite different

Author's difference Thomas Buseries, Thomas Shuerries, Camarack, University of Cambridge, Cambridge, Clark Rina Campbell, Brain Campbell, Brain Campbell, Brain Campbell, Brain Cambridge, Clark Editorshap, H.K. Thomas Sevell, Thomas, Sci. Homes, Sevell, Camarack, Horverity of Cambridge, Clark Cambridge, UK, Alashair Armstrongell camarack, University of Cambridge, UK, Alashair Camb

Version of 2021-09-06 08:49.

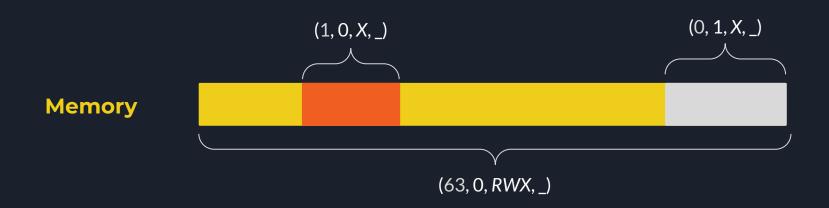

# RISC-V PMP Example

## Verifying MinimalCaps' Security Guarantees

```

{ (\exists c, pc \mapsto c * \mathcal{V}(c) * CorrectPC(c)) * (*_{r \in GPR} \exists w. r \mapsto w * \mathcal{V}(w))}

function exec sd(rs : GPR, rb : GPR, immediate : int) : bool :=

{ rb \mapsto base_cap * \mathcal{V}(base_cap) * rs \mapsto w * \mathcal{V}(w) * \mathcal{V}(c) ...}

call write mem c w ;;

{ rb \mapsto base_cap * \mathcal{V}(base_cap) * rs \mapsto w * \mathcal{V}(w) * \mathcal{V}(c) ...}

call update pc ;; true

\{(\exists c, pc \mapsto c * (\mathcal{V}(c) \lor \epsilon(c))) * (*_{r \in GPR} \exists w. r \mapsto w * \mathcal{V}(w))\}

```

## Contract Execute

```

(\exists c, pc \mapsto c * \mathcal{V}(c) * Correct PC(c)) * (*_{r \in GPR} \exists w. r \mapsto w * \mathcal{V}(w))

function execute() : bool :=

let c := call read_reg_cap pc in

Fetch

let n := call read mem c in

match n with

I inI n =>

Decode

let i := call decode n in

call exec instri

Execute

| inr c => fail

end

{ wp fdeCycle T }

```

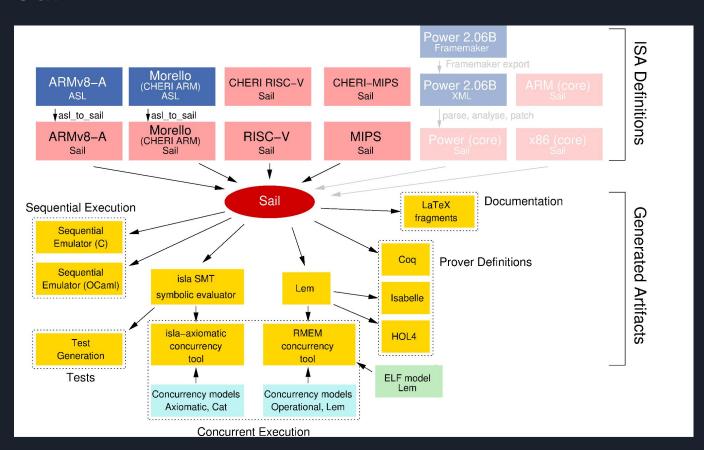

## Future Work

### CCS'22 Submission

Proof Object Virtual Capability Larger ISAs Complex ISAs Realistic ISAs **RISC-V PMP** Capabilities Automation Memory Safety Verification of Capability safety Memory integrity Add support for Further improve Scale up the Introduce Verify security of the for RISC-V PMP object proof number of features such as properties of real security MinimalCaps capabilities to properties of automation of instructions in ISAs, i.e. with concurrency, machine the MinimalCaps Virtual Memory ISAs we interrupts, ... RV32G..., synchronous Katamaran CHERI-RISC-V, ... interrupts case study consider